# High-Performance Low-Cost Back-Channel-Etch Amorphous Gallium–Indium–Zinc Oxide Thin-Film Transistors by Curing and Passivation of the Damaged Back Channel

Jae Chul Park,<sup>†</sup> Seung-Eon Ahn,<sup>‡</sup> and Ho-Nyeon Lee\*,<sup>§</sup>

<sup>†</sup>Institute of Physics and Applied Physics, Yonsei University, Seoul 120-749, Korea

<sup>‡</sup>Semiconductor Device Laboratory, Samsung Advanced Institute of Technology, Yongin-si 446-712, Korea

<sup>§</sup>Department of Display and Electronic Information Engineering, Soonchunhyang University, Asan 336-745, Korea

**Supporting Information**

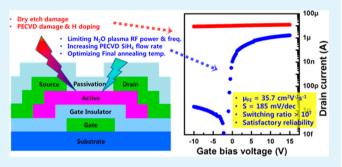

**ABSTRACT:** High-performance, low-cost amorphous gallium—indium—zinc oxide (a-GIZO) thin-film-transistor (TFT) technology is required for the next generation of active-matrix organic light-emitting diodes. A back-channeletch structure is the most appropriate device structure for highperformance, low-cost a-GIZO TFT technology. However, channel damage due to source/drain etching and passivationlayer deposition has been a critical issue. To solve this problem, the present work focuses on overall back-channel processes, such as back-channel N<sub>2</sub>O plasma treatment, SiO<sub>x</sub> passivation deposition, and final thermal annealing. This work has revealed

the dependence of a-GIZO TFT characteristics on the N<sub>2</sub>O plasma radio-frequency (RF) power and frequency, the SiH<sub>4</sub> flow rate in the SiO<sub>x</sub> deposition process, and the final annealing temperature. On the basis of these results, a high-performance a-GIZO TFT with a field-effect mobility of 35.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a subthreshold swing of 185 mV dec<sup>-1</sup>, a switching ratio exceeding 10<sup>7</sup>, and a satisfactory reliability was successfully fabricated. The technology developed in this work can be realized using the existing facilities of active-matrix liquid-crystal display industries.

**KEYWORDS:** annealing, back-channel etch, field-effect transistor, gallium-indium-zinc oxide,  $N_2O$  plasma, passivation

# INTRODUCTION

Amorphous oxide semiconductor (AOS) thin-film transistors (TFTs) are expected to become a major TFT technology<sup>1-7</sup> because of their high performance and low production costs compared to other TFT technologies. The high field-effect mobility ( $\mu_{\rm FE}$ ) of AOS TFTs makes it possible to substitute these transistors for polycrystalline silicon TFTs (poly-Si TFTs) as switching devices for active-matrix organic lightemitting diodes (AMOLEDs). Generally speaking, a  $\mu_{FE}$  value higher than 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> can easily be obtained for AOS  $\overline{TFTs}$ , <sup>4-6</sup> and such a value is high enough for the pixel-driving circuits of AMOLEDs. Additionally, the production costs of AOS TFTs can be kept as low as those of amorphous silicon (a-Si) TFTs because their fabrication processes are similar. Therefore, both the high performance of poly-Si TFTs and the low production costs of a-Si TFTs can be simultaneously realized by AOS TFTs. Moreover, AOS TFTs can be used for novel devices such as transparent displays and smart windows, thanks to the transparency of AOS.<sup>7</sup>

Among the various AOS TFTs, amorphous galliumindium-zinc oxide (a-GIZO) TFTs have received the most attention<sup>1,3,5,10,11</sup> because the process window for obtaining a-GIZO TFTs with suitable switching performance and stability is wider than those of other AOS TFTs. Numerous reports have been published about high-performance, stable a-GIZO TFTs,<sup>11-13</sup> and commercialization of a-GIZO TFTs has recently been undertaken by active-matrix flat-panel display (AMFPD) industries. In the AMFPD market, product pricing is one of the most essential factors. Hence, the lower the production costs are, the better the market penetration of a-GIZO TFTs will be. Two types of device structures are available for typical a-GIZO TFTs: etch stopper  $(ES)^{12,14,15}$ and back-channel etch (BCE).  $^{16-18}$  The ES structure facilitates the fabrication of high-performance, stable a-GIZO TFTs because the ES protects the back channel from damage caused by upper-layer processing.<sup>14,19</sup> However, the device structure of ES TFTs is more complex, and the production costs are higher than those of BCE TFTs. Therefore, it is important to develop a BCE a-GIZO TFT technology that provides a level of performance suitable for commercial AMFPDs. A source/drain dry-etch method is more appropriate than a wet-etch method for fabricating high-resolution AMFPDs, and a passivation layer is required to protect the channel layer of an a-GIZO TFT from the external environment. Hence, these procedures should be

ACS Publications © 2013 American Chemical Society

Received: May 11, 2013 Accepted: November 12, 2013 Published: November 12, 2013

included in the BCE a-GIZO TFT technology. Moreover, in the BCE a-GIZO TFT fabrication process, source/drain dry etching<sup>20,21</sup> and passivation-layer deposition<sup>22,23</sup> are closely related to device performance degradation. To reduce the degradation and obtain a proper switching performance, backchannel  $N_2O$  plasma treatment has been suggested and has proven to be effective.<sup>20,24</sup> In addition to the performance improvement, the device stability is also improved by N2O plasma treatment.<sup>25</sup> Some reports have focused on passivation layers for BCE a-GIZO TFTs.<sup>23,26</sup> However, to establish BCE a-GIZO TFT technology for commercial mass production, it is necessary to systematically study the upper-layer fabrication processes on the back channel. The back-channel treatment, passivation-layer deposition, and final annealing processes should be included in this kind of research because all of these steps influence the back-channel properties. To our knowledge, no papers have been published about this issue.

In this study, we investigated the effects of upper-layer fabrication processes on the device performance of BCE a-GIZO TFTs. To understand the degradation mechanism of the source/drain BCE dry-etch process, the changes in the composition and oxygen binding energy of the a-GIZO active layers were examined because these may have been altered by the source/drain dry-etch and back-channel treatment. The device characteristics of a-GIZO TFTs were then investigated according to the upper-layer process conditions. In this way, we were able to discover key factors determining the device characteristics and obtain high-performance BCE a-GIZO TFTs with high-resolution source/drain features.

#### EXPERIMENTAL SECTION

The device characteristics of a-GIZO TFTs were analyzed with respect to the fabrication process conditions for the upper layers of the a-GIZO active layer. A BCE structure was employed for the a-GIZO TFTs in this work. A back-channel  $N_2O$  plasma treatment was used to restore the performance of a-GIZO channel layers degraded by the source/drain dry-etch process. The effects of back-channel treatment, passivation-layer fabrication, and final annealing on the device characteristics of these TFTs were studied under various process conditions.

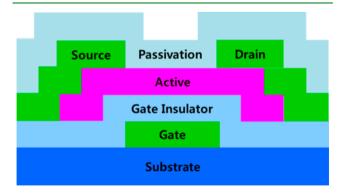

Figure 1 shows a cross-sectional diagram of the type of a-GIZO TFT used in this study. A BCE bottom-gate, top-contact structure,

Figure 1. Cross-sectional diagram of the type of a-GIZO TFT used in this study.

which is the commonest structure for active-matrix liquid-crystal displays (AMLCDs),<sup>27</sup> was employed. The a-GIZO TFTs were fabricated on 6-in. thermally grown silicon dioxide/silicon substrates. After initial cleaning, a molybdenum (Mo) gate metal layer with a thickness of 150 nm was sputtered at room temperature. Gate electrode patterns were then created via a dry-etch process. An

amorphous silicon oxide  $(SiO_x)$  gate insulator layer with a thickness of 100 nm was deposited on the gate electrode, using plasma-enhanced chemical vapor deposition (PECVD) at 150 °C. On the gate insulator, a GIZO active layer with a thickness of 70 nm was deposited via radiofrequency (RF) magnetron sputtering at room temperature. The GIZO target composition was a molar ratio of 1:1:1 Ga<sub>2</sub>O<sub>3</sub>/In<sub>2</sub>O<sub>3</sub>/ ZnO, and the mixing ratio of the sputtering gas was 100:1 Ar/O2. Next, active-island patterns were fabricated, using a wet-etch method with diluted hydrofluoric acid. A layer of Mo with a thickness of 200 nm was sputtered on the active island at room temperature. Source/ drain patterns were fabricated via a dry-etch process. A SF<sub>6</sub>/O<sub>2</sub> gas mixture was used for dry etching of the Mo layer; the overetch time was 60 s. Back-channel treatment with N2O plasma was then conducted. After the back-channel treatment, a 200-nm SiO<sub>x</sub> passivation layer was deposited without a vacuum break via PECVD at 150 °C and then patterned via a dry-etch method. After the device structure fabrication was completed, final annealing was conducted in a nitrogen atmosphere. The device structure, process sequence, and process equipment employed in the fabrication of the BCE a-GIZO TFTs were the same as those used to fabricate a-Si TFTs.

Transfer curves of the fabricated TFTs were measured using a semiconductor parameter analyzer (Agilent 4156B) in a dark shielding box. X-ray photoelectron spectroscopy (XPS) was conducted to examine the composition changes of the a-GIZO films according to the process conditions, using a PHI Quantum 2000.

#### RESULTS AND DISCUSSION

Device characteristics of a-GIZO TFTs were examined under various process conditions for back-channel treatment, passivation-layer deposition, and final annealing. Additionally, composition variations of the a-GIZO active layers due to source/drain dry etching and  $N_2O$  back-channel treatment were investigated. The results were analyzed to identify the optimal fabrication conditions for high-performance BCE a-GIZO TFTs.

Figure 2 shows variation of the composition and oxygen binding energy of the a-GIZO active layers depending on the source/drain dry-etching and N2O back-channel treatment conditions. XPS measurements were conducted using a 1486.6eV monochromatic Al K $\alpha$  X-ray with a beam size of 100  $\mu$ m. To enhance the bulk sensitivity of the measurements, normal emission was used as the takeoff angle. Figure 2a presents the atomic concentrations of the a-GIZO films according to the treatment conditions. These atomic concentrations were obtained from XPS analysis. Figure 2b shows deconvoluted XPS spectra of the O 1s level. The O 1s spectra were deconvoluted into three Gaussian peaks centered at ~529.8 eV (P1), ~530.8 eV (P2), and ~531.6 eV (P3), which were assigned to oxide without oxygen deficiencies, oxide with oxygen deficiencies, and hydroxide, respectively.<sup>28-30</sup> An asdeposited film (A) was included in the composition change analysis as a reference. A source/drain etch plasma-treated film (B) was analyzed to determine the cause of device degradation resulting from the source/drain dry-etch process. A source/ drain etch plasma using an  $SF_6/O_2$  gas mixture was applied to the a-GIZO film for 60 s, which is equal to the overetch time for the source/drain etching process. Because a-GIZO has high etch selectivity, virtually no thickness change resulted from this plasma treatment. The source/drain etch plasma decreased the oxygen concentration and increased the indium and zinc concentrations, as shown in Figure 2a. The increased metallic components may create a conductive backside layer, which, in turn, could degrade the device performance.<sup>20,21'</sup> As shown in Figure 2b, the amount of oxide with deficiencies increased following the etch, whereas the amount of oxide without

Figure 2. (a) Composition variations and (b) deconvoluted O 1s XPS spectra of the BCE a-GIZO active layers according to source/drain dry-etching and  $N_2O$  back-channel treatment conditions: as-deposited film (A); source/drain etch plasma-treated film (B);  $N_2O$  plasma films treated for 60 s (C), 120 s (D), and 180 s (E).

deficiencies decreased. In addition, a hydroxide peak appeared. The increase in the oxygen deficiencies and hydrogen incorporation may have increased the charge carrier density, which may have led to the large off-currents of the TFTs. N<sub>2</sub>O plasma treatment was applied to the source/drain etch plasmatreated samples. The N2O plasma treatment times of samples C-E were 60, 120, and 180 s, respectively. As the N<sub>2</sub>O plasma treatment proceeded, the oxygen concentration increased, and the indium, zinc, and gallium concentrations decreased, as shown in Figure 2a. Figure 2b shows that the N2O plasma treatment restored the O 1s XPS spectrum of the source/drain etch plasma-treated a-GIZO to the original form of the asdeposited a-GIZO. Peak P3 was removed by the 60 s N<sub>2</sub>O plasma treatment. Furthermore, peak P2 was restored to the shape of as-deposited a-GIZO following the 60 s N<sub>2</sub>O plasma treatment. The O 1s XPS spectrum was restored to that of asdeposited a-GIZO by N2O treatment for a duration of more than 120 s. The reactive oxygen supplied by the N<sub>2</sub>O plasma could oxidize metallic or suboxidized metal components, which could result in restoration of the O 1s XPS spectrum, an increase in the oxygen concentration, and a decrease in the metallic concentration. The decrease in the metallic concentration and oxygen deficiency may reduce the conductivity of the a-GIZO film and restore device performance.

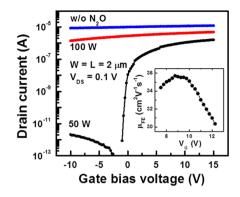

The dependency of the device performance on the RF power of the N<sub>2</sub>O plasma was investigated (see Figure 3). The nearly flat transfer curve of the a-GIZO TFT without N<sub>2</sub>O plasma treatment revealed that the switching performance of the a-GIZO TFT was completely degraded by the source/drain etch plasma. An N<sub>2</sub>O plasma treatment with mild RF power (50 W) restored this degraded performance to a high performance. The field-effect mobility ( $\mu_{\rm FE}$ ), threshold voltage ( $V_{\rm TH}$ ), and subthreshold swing (S) were 35.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, -3.14 V, and

**Figure 3.** Drain currents of the BCE a-GIZO TFTs as functions of gate bias voltage according to the RF power of the N<sub>2</sub>O plasma treatment. The drain bias voltage was 0.1 V, and the source was grounded. The channel width and length were both 2  $\mu$ m.

185 mV dec<sup>-1</sup>, respectively. A linear-mode gradual-channel approximation was used for the evaluation, and  $\mu_{\rm FE}$  was calculated via the equation

$$\mu_{\rm FE} = \frac{\partial I_{\rm D}}{\partial V_{\rm G}} \frac{L}{W C_{\rm GI} V_{\rm D}} \tag{1}$$

where  $I_D$ ,  $V_D$ ,  $V_G$ , L, W, and  $C_{\rm GI}$  are the drain current, drain bias voltage, gate bias voltage, channel length, channel width, and gate insulator capacitance per unit area, respectively. This result is shown as the inset of Figure 3. The value of  $\mu_{\rm FE}$  was obtained by taking the maximum of the calculated values.  $V_{\rm TH}$  was obtained via a linear fitting of measured data to the equation

$$I_{\rm D} = \frac{W}{L} C_{\rm GI} \mu_{\rm FE} (V_{\rm G} - V_{\rm TH}) V_{\rm D}$$

<sup>(2)</sup>

In contrast with the 50 W N<sub>2</sub>O plasma-treated case, the a-GIZO TFT treated with high-RF-power (100 W) N<sub>2</sub>O plasma had no switching capability. N<sub>2</sub>O is preferable to O<sub>2</sub> for backside plasma treatment of BCE a-GIZO TFTs because the enthalpy of oxygen formation is considerably lower for N2O (1.73 eV) than for O<sub>2</sub> (4.13 eV). This comparatively easy formation of oxygen from N2O could reduce ion-bombardment damage during the backside treatment. Hence, the highperformance a-GIZO TFT could be fabricated using 50 W N<sub>2</sub>O plasma treatment. However, even with N2O gas, high-RF-power plasma treatment can induce damage and degrade the device performance, as in the case of the 100 W N<sub>2</sub>O-plasma-treated a-GIZO TFT in Figure 3. Consequently, by adopting N<sub>2</sub>O plasma back-channel treatment and restricting its RF power, BCE a-GIZO TFTs with a suitable switching performance can be obtained.

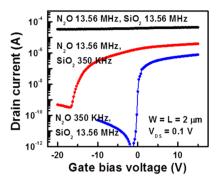

The dependence of the device performance on the RFs of the N<sub>2</sub>O plasma treatment and SiO<sub>x</sub> passivation-layer deposition was examined. Devices were fabricated using a 120 s N<sub>2</sub>O plasma treatment and a 200 nm SiO<sub>x</sub> passivation layer. Figure 4 shows the transfer curves of the BCE a-GIZO TFTs according to the RFs. When the RFs of the N<sub>2</sub>O treatment and SiO<sub>x</sub> deposition were both as high as 13.56 MHz, the switching capability was completely eliminated. When the RF of the N<sub>2</sub>O treatment was as high as 13.56 MHz and the RF of the SiO<sub>x</sub> deposition was as low as 350 kHz, the switching performance of the a-GIZO TFT was rather poor. However, the BCE a-GIZO TFT fabricated with an N<sub>2</sub>O treatment RF of 350 kHz and an SiO<sub>x</sub> deposition RF of 13.56 MHz exhibited a high switching performance. The values of  $\mu_{\rm FE}$ ,  $V_{\rm TH}$  and S for this device were

**Figure 4.** Drain currents of the BCE a-GIZO TFTs as functions of gate bias voltage according to the RFs of the N<sub>2</sub>O plasma treatment and SiO<sub>x</sub> passivation-layer deposition. The drain bias voltage was 0.1 V, and the source was grounded. The channel width and length were both 2  $\mu$ m.

33.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, -3.52 V, and 195 mV dec<sup>-1</sup>, respectively. High-RF plasma causes large ion flux with high ion energy,<sup>31</sup> so the high-RF N<sub>2</sub>O plasma treatment can induce ion bombardment damage. Hence, a-GIZO TFTs with high-RF (13.56 MHz) N<sub>2</sub>O plasma treatment had poor switching properties. Damage caused by the intense N<sub>2</sub>O plasma can increase the leakage current of the a-GIZO TFTs, as shown in Figure 3. In the case of 13.56 MHz N<sub>2</sub>O and 13.56 MHz SiO<sub>x</sub>, the high RF (13.56 MHz) of the SiO<sub>x</sub> deposition process can result in a large energetic hydrogen flux, which may further increase the leakage current because of the role of hydrogen as a donor. In the case of 13.56 MHz N<sub>2</sub>O and 350 kHz SiO<sub>x</sub>, the reduced flux and energy of hydrogen in the SiO<sub>x</sub> deposition process can result in better switching properties than those in the case of 13.56 MHz SiO<sub>x</sub>. When a dry-etch-damaged a-GIZO layer is cured using an appropriate plasma treatment, the resistivity of the a-GIZO layer increases<sup>21</sup> with the incoming excess of oxygen atoms in the layer. These excess oxygen atoms can act as acceptors.<sup>32,33</sup> Hence, hydrogen donors could be counterbalanced by oxygen acceptors. Thus, 350 kHz N<sub>2</sub>O plasma, as an appropriate plasma condition, could cure the dry-etch damage of a-GIZO layers as well as prevent hydrogen-related degradation. Therefore, a high-performance a-GIZO TFT, with 350 kHz N<sub>2</sub>O and 13.56 MHz SiO<sub>21</sub> can be achieved.

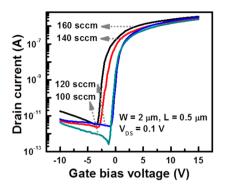

The dependency of device characteristics on the SiH<sub>4</sub> flow rate during the  $SiO_x$  deposition process was examined. Hydrogen acts as a dopant in a-GIZO.<sup>28,33,34</sup> Hence, hydrogen incorporation into an a-GIZO layer during the SiO<sub>x</sub> deposition process increases the conductivity of the layer. SiH<sub>4</sub> is the hydrogen source in the SiO<sub>x</sub> deposition process. Figure 5 shows the transfer curves of the BCE a-GIZO TFTs according to the  $SiH_4$  flow rate. In the SiO<sub>x</sub> deposition process, a gas mixture of SiH<sub>4</sub>, N<sub>2</sub>, and N<sub>2</sub>O was used. The flow rates of N<sub>2</sub> and N<sub>2</sub>O were fixed at 240 and 1420 sccm, respectively, while the flow rate of SiH<sub>4</sub> was varied. The process pressure and RF were 550 mTorr and 350 kHz, respectively, for all devices shown in Figure 5. An increase in the SiH<sub>4</sub> flow rate caused  $V_{\rm TH}$  to shift in the negative direction. Specifically,  $V_{\rm TH}$  was shifted from +2.69 to -0.55 V, and  $\mu_{\rm FE}$  increased from 15.02 to 20.63 cm<sup>2</sup>  $V^{-1}\ s^{-1}$  as the  $SiH_4$  flow rate was increased from 100 to 160 sccm. In addition, the off-current tended to increase with the SiH<sub>4</sub> flow rate. The doping effect of hydrogen may cause a higher carrier concentration at a higher SiH<sub>4</sub> flow rate, and a higher carrier concentration increases the mobility of a-GIZO.  $^{35,36}$  This could explain the  $V_{\rm TH}$  negative shift and the

**Figure 5.** Drain currents of the BCE a-GIZO TFTs as functions of gate bias voltage according to the SiH<sub>4</sub> flow rate during the SiO<sub>x</sub> deposition process. The drain bias voltage was 0.1 V, and the source was grounded. The channel width and length were 2 and 0.5  $\mu$ m, respectively.

$\mu_{\text{FE}}$  increase with increasing SiH<sub>4</sub> flow rate. Additionally, the high carrier concentration may have been related to the high off-current that accompanied the high SiH<sub>4</sub> flow rate.

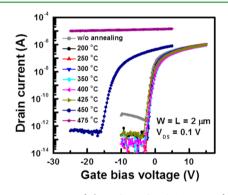

Next, the effects of the final annealing temperature on the device performance of BCE a-GIZO TFTs were investigated. Figure 6 presents the transfer curves of the BCE a-GIZO TFTs

**Figure 6.** Drain currents of the BCE a-GIZO TFTs as functions of gate bias voltage according to the final annealing temperature. The drain bias voltage was 0.1 V, and the source was grounded. The channel width and length were both 2  $\mu$ m.

according to the final annealing temperature. The annealing was conducted in an N<sub>2</sub> atmosphere for 1 h. At annealing temperatures of less than 425 °C, the shape of the transfer curve was virtually unchanged, except for a slightly positive  $V_{\rm TH}$  shift as the annealing temperature increased. However, the off-current was significantly reduced by thermal annealing, compared with what was obtained without annealing. The defect-curing effect of the thermal energy may have been responsible for reducing the off-current. At temperatures above 425 °C, the final annealing significantly degraded the switching performance. The a-GIZO TFT annealed at 450 °C suffered a large negative  $V_{\rm TH}$  shift, while 475 °C annealing completely eliminated the switching capability.

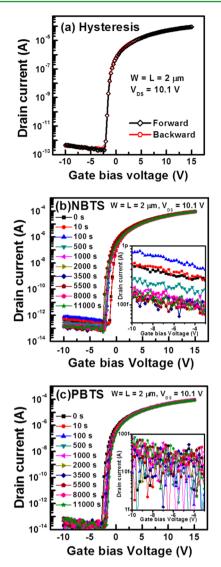

Hysteresis, negative-bias temperature stress (NBTS), and positive-bias temperature stress (PBTS) behaviors were examined (see Figure 7) using the a-IGZO TFTs developed in this work. As shown in Figure 7a, the forward- and reversedirection transfer curves were almost identical. The drain-tosource bias voltage ( $V_{\rm DS}$ ) was 10.1 V, which is sufficiently high compared with the conventional bias voltage for AMFPD applications. Hence, the a-GIZO TFTs seem to exhibit no

**Figure 7.** Transfer curves of a-GIZO TFTs obtained from reliability testing for (a) hysteresis, (b) NBTS, and (c) PBTS. The drain bias voltage was 10.1 V, and the source was grounded during measurements. The channel width and length were both 2  $\mu$ m.

hysteresis properties. Parts b and c of Figure 7 present the results of NBTS and PBTS, respectively. The drain bias voltage  $(V_{\rm D})$ , the source bias voltage  $(V_{\rm S})$ , the gate bias voltage  $(V_{\rm G})$ , and the temperature during NBTS were 10 V, 0 V, -20 V, and 60 °C, respectively, and  $V_D$ ,  $V_S$ ,  $V_G$ , and the temperature during PBTS were 10 V, 0 V, 20 V, and 60 °C, respectively. All transfer curves in Figure 7b,c were measured with  $V_{\rm DS}$  at 10.1 V. For NBTS,  $V_{\text{TH}}$  shift ( $\Delta V_{\text{TH}}$ ) was saturated at -1 V after 100 s, and for PBTS,  $\Delta V_{\rm TH}$  was saturated at 0.75 V after 100 s. These  $\Delta V_{\rm TH}$  values were considerably smaller than those in previous reports.<sup>37–41</sup> To understand the leakage current properties, the off-state drain currents are shown in the insets of Figure 7b,c. For NBTS, the leakage current initially decreased with increasing stress time and finally saturated at approximately  $10^{-13}$  A after a stress period of 1000 s. For PBTS, the leakage current was on the order of  $10^{-14}$  A for all stress times. Therefore, the leakage current was stable in response to the bias stress.

# CONCLUSIONS

The objective of our research was to establish a fabrication process for high-performance BCE a-GIZO TFTs with highresolution features that is comparable to the process used for a-Si TFTs, in terms of both economics and practicality. For this purpose, we used a BCE bottom-gate top-contact structure, and the dependence of the device performance on the upper-layer fabrication processes was investigated.

By optimization of the upper-layer fabrication processes, including the N<sub>2</sub>O backside plasma treatment, passivation-layer deposition, and final annealing, the damage to the channel due to the source/drain dry etch and passivation deposition could be cured and prevented. To achieve this, the RF power and frequency of the N<sub>2</sub>O plasma should be as low as 50 W and 350 kHz. A high-SiH<sub>4</sub>-flow-rate passivation deposition process combined with the final annealing increased  $\mu_{\rm FE}$  without an increase in the leakage current. The a-GIZO TFTs had a field-effect mobility of  $\mu_{\rm FE} = 35.7$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a subthreshold slope of S = 185 mV dec<sup>-1</sup>, and a switching ratio in excess of 10<sup>7</sup>. In addition,  $\Delta V_{\rm TH}$  due to NBTS and PBTS was small compared with that of previous reports.

As the commercialization of a-GIZO TFTs proceeds, the demand for a commercial production technology for highresolution bottom-gate top-contact BCE a-GIZO TFTs is increasing. However, this demand cannot be met using the fabrication methods of previous researches, which focus on unit processes, such as back-channel treatments<sup>20,24,25</sup> and exotic passivation materials.<sup>11,41,42</sup> In this study, we were able to meet this demand successfully by optimizing the overall processes, including the source/drain dry etch, back-channel plasma treatment, passivation deposition, and final annealing. Our devices performed better than commercially available ES a-GIZO TFTs, and the metrics are sufficient for high-quality AMFPD applications. In addition to the high performance, the short channel length (down to 0.5  $\mu$ m) makes our devices appropriate for integrating high-density peripheral circuits on substrates. In addition, the device fabrication process was similar to that of conventional a-Si TFTs for AMLCDs. Hence, our fabrication process may be a core technology in the conversion of existing a-Si TFT production lines to a-GIZO TFT production lines. Therefore, we expect this work to be useful for AMFPD industries in developing competitive baseline technologies for next-generation products.

## ASSOCIATED CONTENT

### Supporting Information

Graphs of the variation ratios of the atomic concentrations of a-GIZO layers and O 1s XPS spectra according to backside treatment conditions, Rutherford backscattering spectrometry spectra showing indium, gallium, and zinc peaks, and scanning electron microscopy images of fabricated BCE a-GIZO TFTs. This material is available free of charge via the Internet at http://pubs.acs.org.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*Tel: +82-41-530-4703. Fax: +82-41-530-1548. E-mail: hnlee@ sch.ac.kr.

#### Notes

The authors declare no competing financial interest.

#### ACS Applied Materials & Interfaces

# ACKNOWLEDGMENTS

This work was supported by the IT R&D program of MKE/ KEIT (10041062, development of fundamental technology for light extraction of OLED) and by the Soonchunhyang University Research Fund.

## REFERENCES

(1) Fortunato, E.; Barquinha, P.; Martins, R. Adv. Mater. 2012, 24, 2945–2986.

(2) Park, J. S.; Maeng, W.-J.; Kim, H.-S.; Park, J.-S. Thin Solid Films **2012**, 520, 1679–1693.

(3) Kamiya, T.; Nomura, K.; Hosono, H. Sci. Technol. Adv. Mater. 2010, 11, 044305-1-044305-23.

(4) Na, J. H.; Kitamura, M.; Arakawa, Y. Appl. Phys. Lett. 2008, 93, 063501-1-063501-3.

(5) Bak, J. Y.; Yang, S.; Ryu, M. K.; Ko Park, S. H.; Hwang, C. S.; Yoon, S. M. ACS Appl. Mater. Interfaces **2012**, *4*, 5369–74.

(6) Park, J. C.; Lee, H.-N. *IEEE Electron Device Lett.* **2012**, 33, 818–820.

(7) Fortunato, E. M. C.; Barquinha, P. M. C.; Pimentel, A. C. M. B. G.; Gonçalves, A. M. F.; Marques, A. J. S.; Pereira, L. M. N.; Martins,

R. F. P. Adv. Mater. 2005, 17, 590-594.

(8) Riedl, T.; Gorrn, P.; Kowalsky, W. J. Disp. Technol. 2009, 5, 501–508.

(9) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. *Nature* **2004**, *432*, 488–92.

(10) Rim, Y. S.; Lim, H. S.; Kim, H. J. ACS Appl. Mater. Interfaces 2013, 5, 3565–3571.

(11) Zan, H.-W.; Yeh, C.-C.; Meng, H.-F.; Tsai, C.-C.; Chen, L.-H. *Adv. Mater.* **2012**, *24*, 3509–3514.

(12) Mativenga, M.; Choi, J. W.; Hur, J. H.; Kim, H. J.; Jang, J. J. Inf. Disp. 2011, 12, 47-50.

(13) Nomura, K.; Kamiya, T.; Hosono, H. Appl. Phys. Lett. 2011, 99, 053505-1-053505-3.

(14) Kim, M.; Jeong, J. H. J. K.; Lee, H. J.; Ahn, T. K.; Shin, H. S.; Park, J.-S.; Mo, Y.-G.; Kim, H. D. *Appl. Phys. Lett.* **2007**, *90*, 212114-1–212114-3.

(15) Li, X.; Xin, E.; Chen, L.; Shi, J.; Zhang, J. AIP Adv. 2013, 3, 032137-1-032137-6.

(16) Lee, J.; Kim, D.; Yang, D.; Hong, S.; Yoon, K.; Hong, P.; Jeong, C.; Park, H.; Kim, S. Y.; Lim, S. K.; Kim, S. S.; Son, K.; Kim, T.; Kwon, J.; Lee, S. Dig. Tech. Pap., Soc. Inf. Disp. Int. Symp. 2008, 39, 625–628.

(17) Chen, T.-C.; Chang, T.-C.; Hsieh, T.-Y.; Tsai, M.-Y.; Chen, Y.-T.; Chung, Y.-C.; Ting, H.-C.; Chen, C.-Y. Appl. Phys. Lett. **2012**, 101,

042101-1–042101-4. (18) Tsai, M.-Y.; Chang, T.-C.; Chu, A.-K.; Chen, T.-C.; Hsieh, T.-Y.; Chen, Y.-T.; Tsai, W.-W.; Chiang, W.-J.; Yan, J.-Y. *Thin Solid Films* **2013**, 528, 57–60.

(19) Geng, D.; Kang, D. H.; Jang, J. IEEE Electron Device Lett. 2011, 32, 758-760.

(20) Park, J.; Kim, S.; Kim, C.; Kim, S.; Song, I.; Yin, H.; Kim, K.-K.; Lee, S.; Hong, K.; Lee, J.; Jung, J.; Lee, E.; Kwon, K.-W.; Park, Y. *Appl.*

Phys. Lett. 2008, 93, 053505-1-053505-3.

(21) Park, J.; Lee, H. Displays 2012, 33, 133-135.

(22) Jeong, J. K.; Won Yang, H.; Jeong, J. H.; Mo, Y.-G.; Kim, H. D. Appl. Phys. Lett. **2008**, 93, 123508-1–123508-3.

(23) Chen, T.-C.; Chang, T.-C.; Hsieh, T.-Y.; Tsai, C.-T.; Chen, S.-C.; Lin, C.-S.; Hung, M.-C.; Tu, C.-H.; Chang, J.-J.; Chen, P.-L. Appl. Phys. Lett. **2010**, *97*, 192103–1–192103–3.

(24) Chang, G.-W.; Chang, T.-C.; Jhu, J.-C.; Tsai, T.-M.; Syu, Y.-E.; Chang, K.-C.; Tai, Y.-H.; Jian, F.-Y.; Hung, Y.-C. *Appl. Phys. Lett.* **2012**, *100*, 182103-1–182103-3.

(25) Hsieh, T.-Y.; Chang, T.-C.; Chen, T.-C.; Tsai, M.-Y.; Lu, W.-H.; Chen, S.-C.; Jian, F.-Y.; Lin, C.-S. *Thin Solid Films* **2011**, *520*, 1427–1431.

(26) Hino, A.; Maeda, T.; Morita, S.; Kugimiya, T. J. Inf. Disp. 2012, 13, 61–66.

(27) Kuo, Y. Electrochem. Soc. Interface 2013, 22, 55-61.

(28) Tsao, S. W.; Chang, T. C.; Huang, S. Y.; Chen, M. C.; Chen, S. C.; Tsai, C. T.; Kuo, Y. J.; Chen, Y. C.; Wu, W. C. Solid-State Electron. **2010**, *54*, 1497–1499.

(29) Jung, S. H.; Moon, H. J.; Ryu, M. K.; Cho, K. I.; Bae, B. S.; Yune, E.-J. J. Ceram. Process. Res. 2012, 13, s246-s250.

(30) Jeong, S.; Ha, Y.-G.; Moon, J.; Facchetti, A.; Marks, T. J. Adv. Mater. 2010, 22, 1346–1350.

(31) Toups, M.; Ernie, D. J. Appl. Phys. 1990, 68, 6125-6132.

(32) Chen, C.; Cheng, K.-C.; Chagarov, E.; Kanicki, J. Jpn. J. Appl. Phys. 2011, 50, 091102-1-091102-10.

(33) Omura, H.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hirano, M.; Hosono, H. J. Appl. Phys. **2009**, 105, 093712-1–093712-8.

(34) Kim, H. J.; Park, S. Y.; Jung, H. Y.; Son, B. G.; Lee, C.-K.; Lee, C.-K.; Jeong, J. H.; Mo, Y.-G.; Son, K. S.; Ryu, M. K.; Lee, S.; Jeong, J.

K. J. Phys. D: Appl. Phys. 2013, 46, 055104-1-055104-6.

(35) Kamiya, T.; Nomura, K.; Hosono, H. J. Disp. Technol. 2009, 5,

(33) Kalinya, 1.; Nolidia, K.; Hosolo, 11. J. Disp. Technol. 2009, 3, 462–467.

(36) Takagi, A.; Nomura, K.; Ohta, H.; Yanagi, H.; Kamiya, T.; Hirano, M.; Hosono, H. *Thin Solid Films* **2005**, *486*, 38–41.

(37) Raja, J.; Jang, K.; Balaji, N.; Choi, W.; Trinh, T. T.; Yi, J. Appl. Phys. Lett. **2013**, 102, 083505-1-083505-4.

(38) Shin, H. S.; Rim, Y. S.; Mo, Y.-G.; Choi, C. G.; Kim, H. J. Phys. Status Solidi A 2011, 208, 2231–2234.

(39) Yoo, D. Y.; Chong, E.; Kim, D. H.; Ju, B. K.; Lee, S. Y. Thin Solid Films 2012, 520, 3788–3786.

(40) Lee, S. K.; Hong, S. II; Lee, Y. H.; Lee, S. W.; Cho, W. J.; Park, J. T. *Microelectron. Reliab.* **2012**, *52*, 2504–2507.

(41) Choi, S.-H.; Jang, J.-H.; Kim, J.-J.; Han, M.-K. *IEEE Electron Device Lett.* **2012**, *33*, 381–383.

(42) Seo, H.-S.; Bae, J.-U.; Kim, D.-W.; Ryoo, C.; Il Kang, I.-K.; Min, S.-Y.; Kim, Y.-Y.; Han, J.-S.; Kim, C.-D.; Hwang, Y.-K.; Chung, I.-J. Dig. Tech. Pap., Soc. Inf. Disp. Int. Symp. 2010, 41, 1132–1135.